LEDを使った通信システムを研究しておりますが、困ってしまう案件がありました。それは送信部ではデータを直列データに変換し、受信部ではもとのデータに戻すシリアライザ、デシリアライザ(SerDes)と呼ばれるものです。研究を始めた当初は光通信のものを用いれば良いかなと思っておりましたが、色々やっていくうちに流用は難しいことが判明。結局VerilogHDLを用いて自作することに。 せっかく作るので、今までオープンソースに色々とお世話になっていたこともあり、これを機にVerilogHDLで作製したSerDesロジックをgithubを用いて公開することを念頭に完全フルスクラッチで開発することにしました。研究室の学生には先行して評価を行ってもらっておりますが、先日通信学会で発表したのでこの投稿ができるわけです。

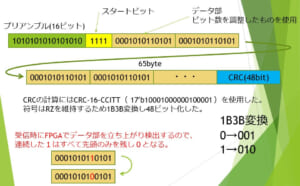

ポイントは8ビットデータを13ビットに符号化するといった単純なものになります。なぜ13ビットかと言えば「1」の後には必ず「0」が来るReturn Zeroにしたかったからです。作製した8B13B SerDesロジックは実用に耐えられるように遅延を用いた同期回路やエラー判定および1ビットまでのエラー訂正もできよう機能を付加しました。

このような工夫をすることでLEDを用いて通信をすることができるようになりました。どのくらいの開発期間がかかったかと申しますと。。。バグ出しを含め授業や卒研指導の合間を使って1年間でした。結構時間がかかります。